Ch4 資料流層次 Dataflow Level

4.1 assign敘述

- 驅動某值至net ( 等號左式只能是net,右式可以是 net 或 reg )

- 資料流層次的描述方式,只能敘述組合邏輯電路( 不含有記憶性電路 )

- 但輸出不可以包含輸入( EX : a = a + b; → 隱含有記憶性 → 錯誤 )

範例:

assign 輸入 = 輸出 ( 可包含運算子 )

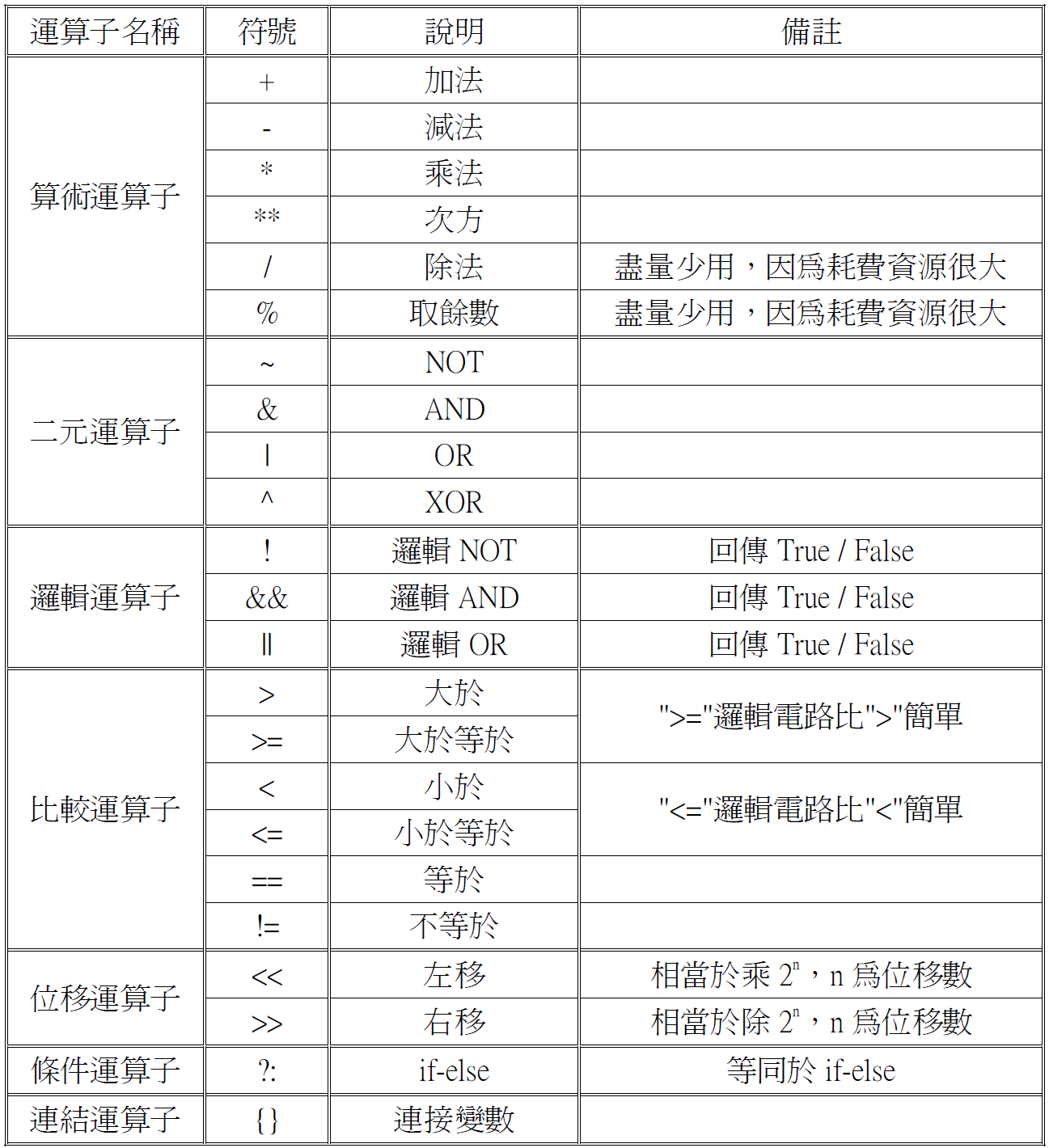

4.2 運算子

4.2.1 條件運算子

範例:

/* 若A>B, Out = A 反之 若A<=B, Out = B */

Out = ( A>B ) ? A : B;

/* 使用if-else */

If( A>B )

Out = A;

else

Out = B;

4.2.2 連結運算子

範例:

A = { 1’b0, 1’b1 }; // A = 2’b01

A = { B[1:0], C[0], D[2] }; // A = B[1], B[0], C[0], D[2]

A = { 2{2’b01} }; // A = 4’b0101

A = { 3’b101, 2{1’b0} } // A = 5’b10100

4.3 實際範例

一位元全加器程式碼:

module Full_Adder( A, B, Cin, Sum, Cout );

input A, B, Cin;

output Sum, Cout;

wire W1, W2, W3;

assign W1 = A^B;

assign W2 = W1&Cin;

assign W3 = A&B;

assign Sum = W1^Cin;

assign Cout = W2|W3;

endmodule